La norme JTAG (Join Test Action Group), IEEE 1149.1 a été publié en 1990. Elle a été élaborée par un groupe de plus de 200 grands fabricants d'électronique avec comme objectifs de fournir, d’une part des règles communes de testabilité des cartes électroniques et d'autre part d’apporter une réponse aux problèmes d’accessibilité dus à l'utilisation intensive de boitiers BGA (Ball Grid Array), de circuits multicouches complexes et de réduction constante des géométries. Cette norme est maintenant utilisée mondialement sur les composants et les cartes électroniques.

RÉSUMÉ

Elle permet de détecter la majorité des défauts de fabrication comme les joints de soudure, les circuits- ouverts ou les courts-circuits très fréquents lors du montage des composants. Par extension, cette norme s’applique également aux systèmes électroniques.

Sur les vingt dernières années, une dizaine d’autres normes sur la testabilité des cartes électroniques ont été publiées toujours dans l’objectif d’augmenter la couverture de test et de réduire les coûts.

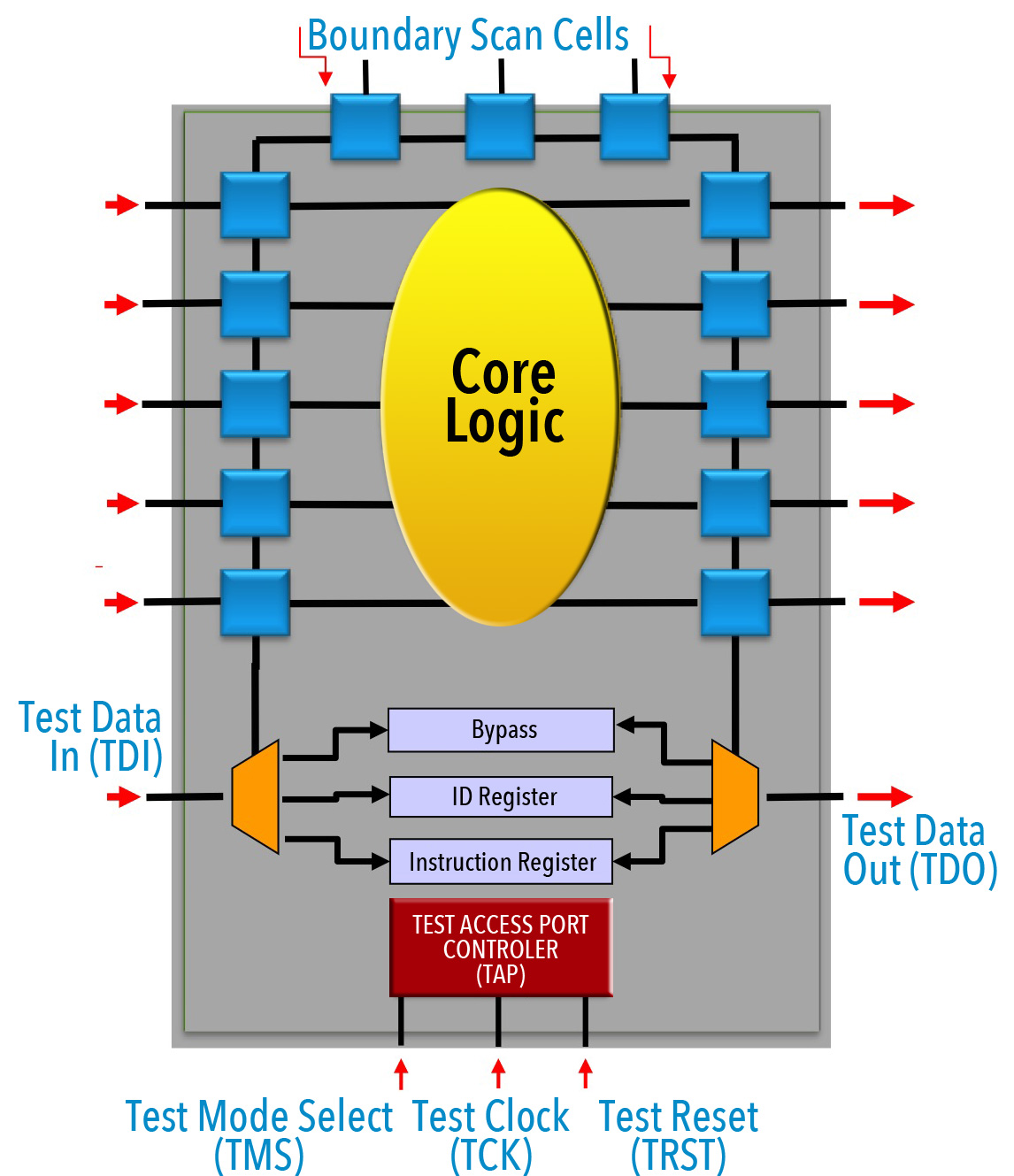

DESCRIPTION

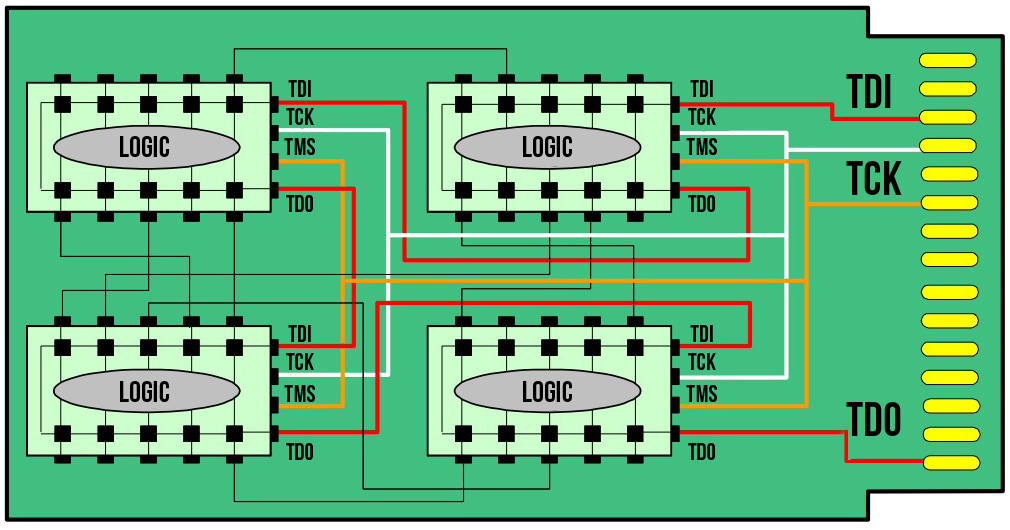

Lors de la conception de la carte, les composants sont chaînés entre eux par le bus de test en mode série. Le bus de données TD0 d’un composant devenant le bus de données d’entrées (TDI) du composant suivant et ainsi de suite, pour former une chaîne JTAG complète.

• TCK •

(Horloge de Test)

• TDI •

(Entrée des données de test)

• TDO •

(Sortie des données de test)

• TMS •

(Sélection du mode de test)

• TRST •

(Remise à zéro de la logique de test) (option).

Lors du test, un simple connecteur 4/5 fils permet d’avoir accès à l’ensemble de la chaine JTAG, pour venir actionner les machines d’états et la logique boundary scan de chaque composant. C’est sur ce principe que ensuite vont pouvoir être développés des tests structurels sur l’ensemble des nets de la carte. Par extension, on pourra également réaliser la programmation des mémoires Flash, du test fonctionnel JTAG, le test des connecteurs, la lecture du registre d’identification de chaque composant, du diagnostic pas à pas etc..

LE COINS DES NORMES

Description:

La norme IEEE Std. 1149.1-1990 pose les bases de la technologie Boundary Scan, avec la description des types de registres à décalage, la description du port d’accès (TAP – Test Access Port), de la machine à état finis et des instructions et commandes de registres.

• www.standards.ieee.org/findstds/standard/1149.1-1990.html

Cette norme a été enrichie et remplacée au cours des années avec les normes suivantes :

• 1149.1a-1993 – Premier supplément à la norme 1149.1.

• 1149.1b-1994 – Deuxième supplément à la norme 1149.1.

• 1149.1- 2001 – Troisième supplément à la norme 1149.1.

Situation: (norme active)

Description:

Cette norme englobe toutes les précédentes et rajoute un langage qui permet une meilleure définition structurelle des fonctions de test des composants et d’utilisation de ces fonctions.

http://standards.ieee.org/findstds/standard/1149.1-2013.html

Situation: (norme active)

Description:

La structure de testabilité pour circuits numériques décrits dans la norme IEEE Std 1149.1-2001 a été étendue aux circuits à signaux mixtes. Cette norme décrit des nouveaux registres ainsi que les moyens de contrôle et d'accès à la fois analogique et aux données de test numériques. Des exemples d’application et de mise en œuvre (qui ne font pas partie de la norme) sont inclus à titre d'illustration. En outre, des extensions spécifiques à la norme BSDL (Boundary Scan Description Language) sont définies.

http://standards.ieee.org/findstds/standard/1149.4-2010.html

Situation: (norme active)

Description:

Cette norme définit les structures de test à utiliser pour le test des liaisons différentielles à couplage capacitif. La norme IEEE 1149.1 répond parfaitement aux besoins de test structurel des composants numériques standards mais reste insuffisante pour le test des signaux LVDS. L’implantation de cette norme 1149.6 dans les composants utilisant des liaisons rapides permet de diagnostiquer rapidement tous défauts éventuels sur ces liaisons.

http://standards.ieee.org/findstds/standard/1149.6-2003.html

Situation: (norme active)

Description:

la norme IEEE 1149.7-2009 appelée cJTAG ou « compact JTAG », a été développée pour les systèmes qui comportent une interface limitée en nombre de broches d’accès dédiées au test (SOC, boitiers 3D, objets embarqués). Toujours basée sur la norme 1149.1. Organisée en un ensemble de six classes, que l'on peut implanter ou non, l'IEEE 1149.7 permet, si on le souhaite, de n'utiliser pour scanner un circuit que deux broches au lieu des quatre nécessaires pour le Jtag traditionnel. Ces deux fils supportent les signaux d'horloge et les données d'E/S, y compris les données et signaux d'instrumentation.

http://standards.ieee.org/findstds/standard/1149.7-2009.html

Situation: (norme active)

Description:

Cette norme définit des extensions d’un certain nombre de structures boundary scan à la norme IEEE Std 1149.1 pour le test des composants passifs, connecteurs et les composants qui ne sont pas traités de manière adéquate par rapport aux normes existantes. Cette norme spécifie également des extensions du lanage Boundary-Scan Description Language (BSDL) nécessaire pour décrire et soutenir les nouvelles structures de test.

http://standards.ieee.org/findstds/standard/1149.8.1-2012.html

Situation: (norme active)

Description:

La norme IEEE 1500 a été créée plus particulièrement pour les SOC (System On Chip) complexes. Elle fournit les éléments techniques pour créer une interface de test (wrapper) ou anneau autour d’une partie logique à l’intérieur d’un ASIC ou SOC. Cette interface de test comporte un ensemble de règles pour un échange de données de test entre le noyau logique et l’anneau de test. La norme IEEE 1500 a été largement influencée par les travaux antérieurs réalisés sur le Std 1149.1 ™.

http://standards.ieee.org/findstds/standard/1500-2005.html

http://grouper.ieee.org/groups/1500/index.html

Situation: (norme retirée)

Description:

Cette norme définit une méthode de programmation pour les composants programmables, (FPGA et CPLD). Elle inclut une série d’instructions et registres associés pour accéder et configurer un composant programmable. Cependant, la norme 1149.1 reste suffisante pour réaliser ces opérations et elle a donc finalement été retirée.

http://standards.ieee.org/findstds/standard/1532-2002.html

Statut (norme active)

Description:

La norme IEEE Std 1581 définit une méthode pour tester les interconnexions des circuits mémoires (DDR2, DDR3 etc.) rapide lorsque la norme 1149.1 se révèle être inefficace. Cette norme décrit les règles de mise en œuvre pour la logique de test et le mode de test d'accès / sortie méthodes de circuits intégrés conformes. La norme est limitée à la description du comportement de la mise en œuvre et ne comprendra pas la conception technique pour la logique de test ou un test de contrôle de mode circuit.

http://standards.ieee.org/findstds/standard/1581-2011.html

Statut (norme active)

Description:

Une méthodologie pour accéder à l'instrumentation embarquée dans un dispositif semi-conducteur, sans définir les instruments ou leurs caractéristiques elles-mêmes, via le port IEEE 1149.1 (TM) de test d'accès (TAP) et / ou d'autres signaux, est décrit dans la présente norme. Les éléments de la méthode comprennent une architecture matérielle du réseau sur puce reliant les instruments aux broches de la puce, un langage de description de matériel pour décrire ce réseau, et un langage de logiciel et le protocole de communication avec les instruments via ce réseau.

http://standards.ieee.org/findstds/standard/1687-2014.html

Les normes en préparation Les projets actifs

Description:

Ce projet de norme définit les caractéristiques d'accès de test pour des composants 3D, les connexions internes et les connexions de circuit à circuit.

Plus d'informations sur http://standards.ieee.org/develop/project/1838.html

Introduction

Cette initiative appelée SJTAG (pour système JTAG) consiste à résoudre un ensemble de problèmes liés au test étendu des cartes utilisant la norme 1149.1 assemblées dans un système. L'objectif est de définir le contenu et formats de données de communication entre les plateformes externes (XBST) et les contrôleurs de tests embarqués sur les cartes (EBST).

Ce projet définit une méthodologie pour l’accès au test, au débogage, à l’instrumentation et/ou à la programmation ainsi qu’aux dispositifs d’émulation pour les systèmes de cartes et ce via la norme 1149.1.

Les éléments de cette méthodologie incluent un langage de description décrivant la façon dont les diverses normes (1149.4, 1149.6, 1532, P1687, 1581) et d’autres mécanismes peuvent tirer parti de l’interface IEEE 1149.1 dans le cadre d’un système multicartes. Sont inclus également une description des formats de représentation des données pour les vecteurs de test, de diagnostic, d’enregistrement des données, et des interfaces de programmation d'applications (API).

http://www.sjtag.org/

Sur le plan des stratégies de test pour la fabrication des systèmes électroniques, le groupe iNEMI travaille sur l’intégration des technologies boundary-scan et d’auto-test intégré (BIST) en vue de la mise en place de normes futures.

L’augmentation de la complexité des produits et la réduction des accès aux points de test conduisent à l’utilisation croissante des technologies BS et BIST pour améliorer la couverture de test. Un groupe projet de l’iNEMI travaille sur ces sujets pour encore améliorer la testabilité des produits électroniques dans le futur.

http://www.inemi.org/project-page/built-self-test-bist-program