L'utilisation intensive des boitiers Ball Grid Array (BGA), 3D et la miniaturisation des géométries réduisent l'accès physique aux broches et aux points de test par les lits de clous traditionnels. Par ailleurs, l'utilisation de composants à haute vitesse comme l'introduction des mémoires dynamiques à double débit de données (DDR3/4) et l’augmentation des fréquences d’horloge demandent également une intégrité et une qualité de signal que ne peuvent plus assurer les lits de clous et testeurs traditionnels.

Les points de blocage

Les solutions TEMENTO - la technologie SpeedScan

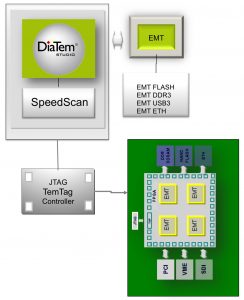

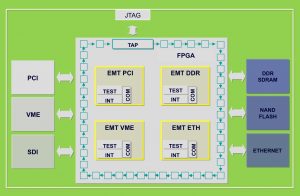

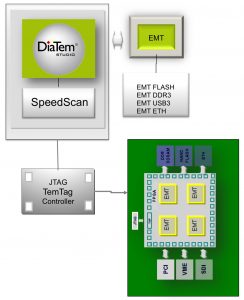

Engagé sur le débogage des cartes électroniques et des composants depuis plus de dix ans, Temento Systems a une longue expérience sur le développement d'instruments embarqués pour FPGA. Déclencheurs, analyseurs logiques et contrôleurs de bus ont été développés et sont disponibles depuis plusieurs années via notre outil de débogage pour FPGA "Dialite". Sur la base de ces acquis technologiques, nous avons ensuite transposé cette connaissance au niveau du test des cartes électroniques. Un Module SpeedScan, intégré dans DiaTem permet d’exécuter les tests fonctionnels dans le même environnement que celui utilisé pour l’exécution des tests JTAG structurels. La technologie SpeedScan offre aussi la possibilité d’incorporer ses propres instruments.

Les Micro Testeurs Embarqués (EMT)

Très tôt, Temento Systems a introduit un nouveau concept appelé MTE pour Micro Testeur Embarqué. Cette technologie appelée "SpeedScan" (*) combine la technologie Boundary Scan et le concept d’instruments embarqués. Un MTE est un « moteur de test » téléchargé dans le FPGA de la carte sous test via le bus JTAG. Il est composé de plusieurs modules logiques capables d'exécuter des algorithmes de test à la vitesse de l’horloge de la carte. Lorsque le test est terminé, le résultat est transmis au contrôleur JTAG et remonté dans notre logiciel de test « Diatem ». Un catalogue d’une vingtaine de types de MTE est maintenant disponible.

(*) Technologie brevetée

Différents MTE ont été développés selon le type de mémoire RAM, DDRSDRAM, SDRAM, à tester etc. Chaque EMT peut être réutilisé pour différentes cartes électroniques. L'algorithme de test mémoire mis en œuvre fonctionne à la vitesse du FPGA.

De la même façon que pour les mémoires, des MTE dédiés « bus » sont disponibles pour tester les bus RS232, CAN, Ethernet, USB etc..

Les mémoires flash peuvent être programmés par le bus JTAG, cependant le temps de programmation étant une fonction de la fréquence d’horloge TCK et de la longueur de la chaîne JTAG, cette technique est limitée pour des fichiers de taille supérieure à quelques centaines de Kilo-Octets. Comme la taille des fichiers est en constante augmentation, nous recommandons l’utilisation des MTE « programmation » ce qui permet de diminuer les temps de programmation d’un facteur X50 à X100.

Des MTE de type « mesure » peuvent également être utilisés par exemple pour la mesure de la fréquence de l’horloge.

@ Speed Test

Charger en temps réel un micro testeur dans le FPGA de votre carte vous apporte des capacités de test fonctionnel encore inégalées !

Les solutions TEMENTO - la technologie EmulScan pour processeurs

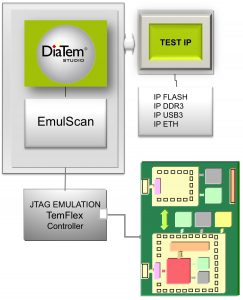

De la même manière que nous avons introduit les tests fonctionnels JTAG pour cartes électroniques à base de FPGA, nous avons développé le concept d’exécution des tests fonctionnels JTAG pour les cartes électroniques comportant des processeurs. Cette technologie appelée "EmulScan" est une façon nouvelle et innovante de faire du test fonctionnel de composants au niveau prototype ou en production. Intégré dans DiaTem le module EmulScan permet de gérer dans le même environnement tests JTAG structurels et tests JTAG fonctionnels. Les familles principales de processeurs CPU-MCU prises en charge sont: ARM7, ARM9, Cortex-M3, Coldfire V1 / V2 / V3 / V4, OMAP, XScale, Power PC etc .. En plus des tests fonctionnels JTAG, l'utilisateur peut exécuter des programmes d’application en C en mode pure émulation comme avec tous les autres environnements d'émulation classique.

Pour parvenir à ce résultat, nous avons combiné la technologie d'émulation de la société iSystems avec notre technologie JTAG – DiaTem. Profitant du bus JTAG de débogage embarqué dans les CPU-MCU, et après une initialisation des registres, un IP de test est téléchargé dans la mémoire du processeur et exécuté par celui-ci. Ainsi, le processeur va tester lui-même l’ensemble des composants périphériques de la carte et renvoyer au logiciel des informations sur le fonctionnement de ces composants.

Des IP de test (Intellectual Property) ont été développés pour tester différents types de mémoire RAM, DDRSDRAM, SDRAM, etc.. Les vitesses d’écriture – lecture sont effectuées à la vitesse et fréquence d’horloge du bus.

Des IP de test pour les bus Ethernet, RS232, USB etc. peuvent être utilisés comme des clusters standards et sont intégrés dans l’environnement de DiaTem.

Entièrement intégré au sein de notre plate-forme ISP Diatem, ces IP de programmation des mémoires Flash NAND et NOR utilisent la puissance et la rapidité des bus et contrôleurs mémoires de chaque processeur pour réaliser ces opérations. Ceci se traduit par une vitesse de programmation accrue et une validation fonctionnelle de leur comportement.